Antes de iniciar, en el artículo cómo funciona una memoria electrónica damos los conceptos básicos y los definiciones las encotrara en memorias electrónicas.

EEPROM o E²PROM

De sisgas Electrically Erasable Programmable Read-Only Memory (ROM programable y borrable eléctricamente). Es un tipo de memoria ROM que puede ser programada, borrada y reprogramada eléctricamente.

- Las celdas de memoria de una EEPROM están constituidas por un transistor MOS, con una compuerta flotante (estructura SAMOS), que proporciona un estado normal cortado y una salida de 1 lógico.

- La EEPROM puede ser leída un número ilimitado de veces, pero solo puede ser borrada y reprogramada entre 100.000 y un millón de veces.

- La comunicación de estos dispositivos se realiza a través de protocolos como I²C, SPI y Microwire.

- A menudo, las EEPROM se integran en chips como microcontroladores y DSPs para aumentar la velocidad de acceso.

- La memoria flash, una forma avanzada de EEPROM, fue creada por el Dr. Fujio Masuoka mientras trabajaba para Toshiba en 1984, y fue presentada en la Reunión de Aparatos Electrónicos del IEEE de 1984.

- Intel lanzó el primer chip comercial de tipo NOR en 1988, reconociendo el potencial de la invención de Masuoka.

Memorias EEPROM de familia 24Cxx

Este es un listado de las memorias mas comunes de la familia 24Cxx con sus capacidades:

| Modelo | Capacidad (bit) | Capacidad (bytes) | Páginas (bytes) | Direcciones I2C disponibles | Notas destacadas |

|---|---|---|---|---|---|

| 24LC01 | 1 Kbit | 128 bytes | 8 | 8 (A0–A2 configurables) | Ideal para datos muy pequeños |

| 24LC02 | 2 Kbit | 256 bytes | 8 | 8 | Muy compacta |

| 24LC04 | 4 Kbit | 512 bytes | 16 | 4 (2 bloques de 256 bytes) | Se accede por bancos con dirección I2C |

| 24LC08 | 8 Kbit | 1 KB | 16 | 2 (4 bloques internos) | Ideal para proyectos medianos |

| 24LC16 | 16 Kbit | 2 KB | 16 | 1 (bloques internos) | Dirección I2C fija: solo 0x50 |

| 24LC32 | 32 Kbit | 4 KB | 32 | 8 | Común en módulos EEPROM para Arduino |

| 24LC64 | 64 Kbit | 8 KB | 32 | 8 | Muy usada en almacenamiento de configuraciones |

| 24LC128 | 128 Kbit | 16 KB | 64 | 8 | Uso profesional, buena para logs |

| 24LC256 | 256 Kbit | 32 KB | 64 | 8 | Frecuente en módulos I2C con zócalo |

| 24LC512 | 512 Kbit | 64 KB | 128 | 8 | Gran capacidad, ideal para registro masivo |

📊 Tabla de funcionamiento de pines A0, A1, A2 en memorias EEPROM 24LCxx

| Modelo | Tamaño (bytes) | Dirección base I2C | Uso de A0–A2 | Nº de direcciones disponibles | Notas especiales |

|---|---|---|---|---|---|

| 24LC01 | 128 | 0x50 – 0x57 |

Sí (A0–A2) | 8 | Todos los bits A0–A2 usados en dirección I2C |

| 24LC02 | 256 | 0x50 – 0x57 |

Sí (A0–A2) | 8 | Igual que 24LC01 |

| 24LC04 | 512 | 0x50, 0x51 |

❌ No usados | 1 chip = 2 bloques I2C | A0–A1 seleccionan bloques internamente, no pines |

| 24LC08 | 1024 | 0x50 – 0x53 |

❌ No usados | 1 chip = 4 bloques I2C | A0–A1 internos, dirección cambia por bloques |

| 24LC16 | 2048 | 0x50 (fijo) |

❌ No usados | 1 | Dirección fija, direccionamiento interno completo |

| 24LC32 | 4096 | 0x50 – 0x57 |

✅ Sí (A0–A2) | 8 | Cada pin A0–A2 aporta un bit a la dirección I2C |

| 24LC64 | 8192 | 0x50 – 0x57 |

✅ Sí (A0–A2) | 8 | Igual a la 24LC32, mayor tamaño |

| 24LC128 | 16384 | 0x50 – 0x57 |

✅ Sí (A0–A2) | 8 | Usa direccionamiento interno de 16 bits |

| 24LC256 | 32768 | 0x50 – 0x57 |

✅ Sí (A0–A2) | 8 | Muy común, ideal para almacenamiento general |

| 24LC512 | 65536 | 0x50 – 0x57 |

✅ Sí (A0–A2) | 8 | Gran capacidad, ideal para dataloggers |

🧠 ¿Qué significan las columnas?

- Uso de A0–A2: indica si los pines físicos A0, A1 y A2 del chip se usan para modificar la dirección I2C.

- Nº de direcciones disponibles: cuántos chips puedes conectar en el mismo bus I2C sin conflictos, cambiando los pines A0-A2.

- Notas especiales: detalla diferencias importantes, como direccionamiento por bloques internos o direcciones fijas.

🔍 Ejemplo práctico

Si usas una 24LC256 y configuras sus pines así:

- Pin Conexión

- A0 GND

- A1 VCC

- A2 GND

Esto equivale a A2 A1 A0 = 0 1 0 → dirección I2C = 0x52

🧠 ¿Cómo funcionan los pines A0, A1 y A2 en la 24LC32?

📦 Dirección base del chip:

El formato de la dirección I2C es:

1 0 1 0 A2 A1 A0 R/W

- Los cuatro bits más significativos (

1010) son fijos para todos los chips 24LCxx. - Los siguientes tres bits (

A2 A1 A0) provienen de los pines físicos del chip. - El bit menos significativo (

R/W) indica si es lectura (1) o escritura (0).

📌 Resultado: puedes configurar hasta 8 direcciones diferentes

| A2 | A1 | A0 | Dirección I2C (hex) |

|---|---|---|---|

| 0 | 0 | 0 | 0x50 |

| 0 | 0 | 1 | 0x51 |

| 0 | 1 | 0 | 0x52 |

| 0 | 1 | 1 | 0x53 |

| 1 | 0 | 0 | 0x54 |

| 1 | 0 | 1 | 0x55 |

| 1 | 1 | 0 | 0x56 |

| 1 | 1 | 1 | 0x57 |

🎯 Ventaja: puedes conectar hasta 8 memorias 24LC32 al mismo ESP32 o Arduino en el mismo bus I2C, siempre que configures correctamente los pines A0–A2.

Comunicación de memoria EEPROM

Las EEPROM se comunica típicamente a través de un bus de comunicación serial, como I²C (Inter-Integrated Circuit), SPI (Serial Peripheral Interface).

Comunicación mediante I²C:

- En el protocolo I²C, la EEPROM actúa como un dispositivo esclavo en el bus.

- El bus I²C tiene dos líneas de comunicación: SDA (Serial Data) y SCL (Serial Clock).

- Para comunicarse con la EEPROM, el dispositivo maestro (generalmente un microcontrolador) envía una secuencia de datos que incluye la dirección de la EEPROM y la operación que se desea realizar (lectura o escritura).

- La EEPROM responde a las solicitudes del maestro y transfiere los datos según sea necesario.

- La velocidad de comunicación en el bus I²C se especifica en términos de frecuencia de reloj y puede variar según las especificaciones del dispositivo.

Comunicación mediante SPI:

- En el protocolo SPI, la EEPROM también puede actuar como un dispositivo esclavo.

- El bus SPI consta de cuatro líneas: SCK (Serial Clock), MOSI (Master Output Slave Input), MISO (Master Input Slave Output) y SS (Slave Select).

- Para iniciar la comunicación, el maestro selecciona la EEPROM tirando del pin SS correspondiente (bajo para activar, alto para desactivar).

- El maestro envía los comandos y datos a la EEPROM a través de las líneas MOSI y SCK, y recibe los datos de vuelta a través de la línea MISO.

- La velocidad de comunicación en el bus SPI se controla mediante la frecuencia del reloj SCK, que puede ser configurada por el maestro según las capacidades de la EEPROM y los dispositivos conectados.

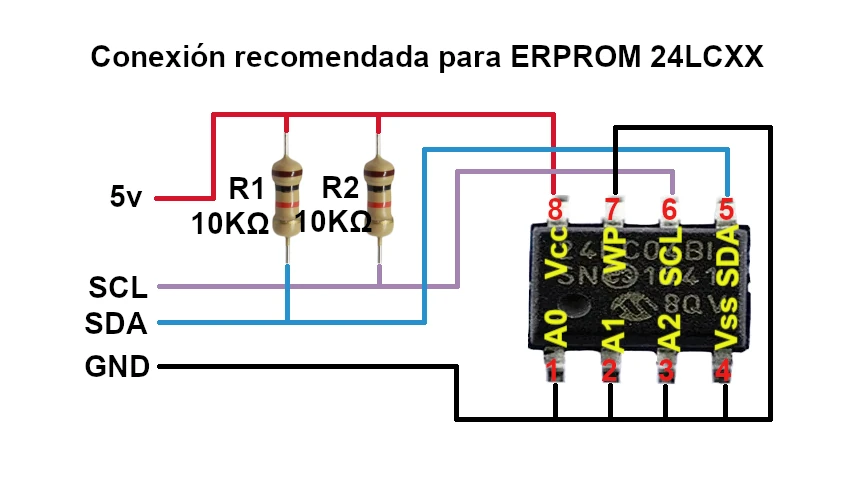

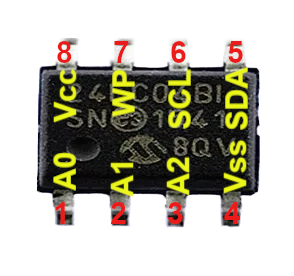

🔌 Conexión recomendada

| Pin | Conexión recomendada | Nota |

|---|---|---|

| A0 | GND | No se usa para dirección |

| A1 | GND | No se usa para dirección |

| A2 | GND | No se usa para dirección |

| WP | GND | Para permitir escritura |